기술은 감각이다, 밀론 블로그

Chapter 5-5 (이온주입) Chaneling, Lattice damage, and annealing, 예제 [반도체공정] feat.jaeger 본문

Chapter 5-5 (이온주입) Chaneling, Lattice damage, and annealing, 예제 [반도체공정] feat.jaeger

milron 2024. 6. 30. 21:29반도체 8대 공정

1. 실리콘 웨이퍼 제조 공정

2. 산화공정(Oxidation)

3. 포토공정(Photo)

4. 식각공정(Etching)

5. 증착공정(Deposition)

6. 금속배선공정(Metalliztion)

7. EDS 공정(Electrical Die Sorting)

8. 패키지공정(Package)

지금까지 이온 주입이 어떻게 이루어지는지 이해하였고 이온 주입에 따른 손실까지 살펴보았습니다.

이번 포스팅에서는 이온이 기판으로 이동할 때 발생하는 현상과 그로 인해 발생되는 격자의 결함에 대해 설명하겠습니다.

5. 증착공정(Deposition) 목차

1. Chapter 5.1~5.2 (이온주입) 주입범위, 예제 [반도체공정] feat.jaeger

2. Chapter 5.3~5.4 (이온주입) 주입 깊이, 핵저지, 전자저지 [반도체공정] feat.jaeger

3. Chapter 5-5 (이온주입) Chaneling, Lattice damage, and annealing, 예제 [반도체공정] feat.jaeger

이온 주입을 진행한다면, 이온이 기판으로 주입되는 과정 속에서 어떤 현상이 발생하는지에 대한 지식과 이해가 필요합니다.

5.5 Chaneling, Lattice damage, and annealing

5.5.1 Ion Chaneling efect(이온 채널링 효과)

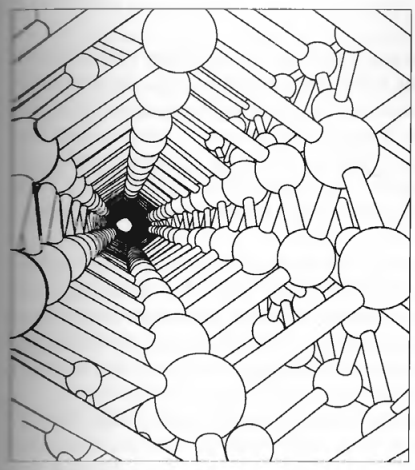

그림 5.7은 실리콘 기판의 방향이 (110)인 모습을 그린 겁니다.

만약 입사이온이 (110) 방향으로 진행된다면?

위 그림의 무한히 이어진 텅 빈 공간을 향해 끝없이 이동해 버릴 겁니다.

우리는 분명 특정 위치에 이온을 주입하고자 했습니다.

그런데 이 Ion Chaneling 현상은 우리의 목표를 방해하여 예측을 어렵게 합니다.

따라서 이는 매우 좋지 않은 현상으로써 반드시 억제되어야 할 현상입니다.

해결 방법은 기판을 기울이는 것입니다.

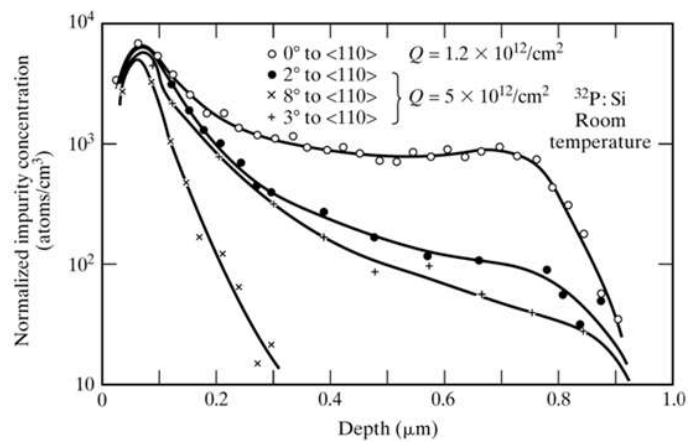

그림 5.8 그래프 x축은 불순물이 주입된 깊이, y축은 주입된 불순물 농도입니다.

주목해야 할 부분은 각도입니다.

입사이온이 기판 (110)을 향해 이동할 때 기판의 각도를 기울여 불순물 농도를 그린 겁니다.

그래프를 보면 7~10도 정도 기울여 줄 때 채널링 현상이 줄어드는 것을 볼 수가 있습니다.

즉 Gauss 분포에 더 가까워지는 겁니다.

그러나 실제 공정에서 기판을 기울인다?

이러한 행위는 낮은 재현성을 발생시킵니다.

수율이 낮아지는 결과가 발생합니다.

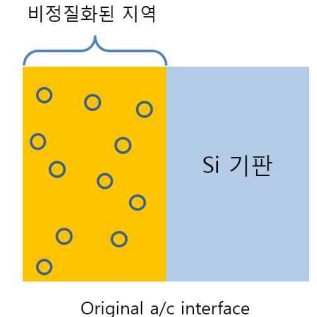

그래서 실질적인 해결법으로 Ar과 같은 불활성 기체를 기판에 선 이온주입하여 마치 금 간 거울처럼 amorphization(비정질화) 시킵니다.

5.5.2 Lattice damage(격자 손상)

nuclear stopping(핵저지)를 기억하시나요?

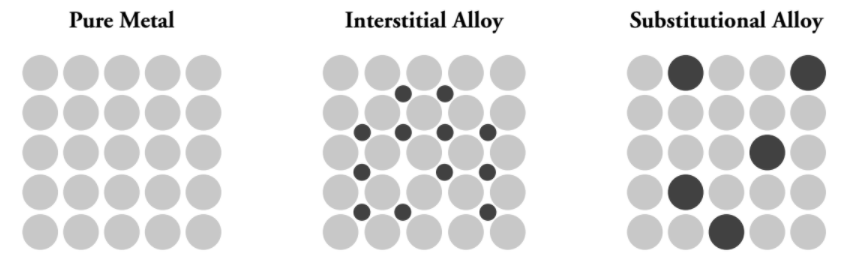

입사이온이 표적 원자를 탄성충돌하여 격자에서 이탈시키는 정의였습니다.

입사이온이 기판의 원자를 때려 이탈시킵니다.

이때 이탈되어 생긴 빈 공간은 vacancy(빈 공간)가 되고 interstitail이 되고,

이렇게 vacancy + interstitail 쌍이 생기게 됩니다.

이러한 쌍을 Frenkel defect 혹은 Frenkel pair라고 부릅니다.

이탈된 원자는 다른 원자와 다시 부딪혀 2차, 3차적으로 Frenkel defect를 일으킬 수 있습니다.

이 현상을 cascade of collisions라고 합니다.

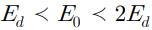

이 격자 이온을 이탈시키는 데 필요한 에너지를 E_d(displacement energy)라고 합니다.

입사에너지 E_0가 E_d보다 크다면?

그 어떤 원자도 이탈시킬 수 없습니다.

이라면 한 원자는 이탈시킬 수 있지만 cascade of collisions는 불가능해집니다.

2E_d보다 높아야 가능합니다.

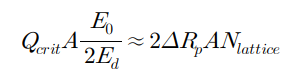

따라서 입사 이온 한 개가 이탈시키는 총 원자 수는 다음과 같이 근사할 수 있습니다.

: Kinchin-Pease formula

Si의 경우 15 eV 정도입니다.

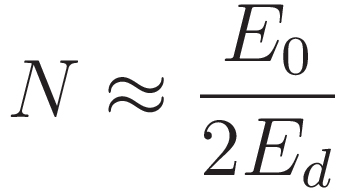

만약 입사이온이 격자 원자보다

가벼운 경우-

전자저지 효과가 더 큽니다.

오른쪽 그림 (a)에 해당합니다.

무거울 경우-

핵저지 효과가 더 큽니다.

오른 쪽 그림 (b)에 해당합니다.

그림 (b)가 이상적인 이온주입의 결과입니다.

다수의 입사 이온폭격으로 손상이 심해져 기판 표면 근처가 amorphous 상태가 되는 것을 아까 설명한 amorphization(비정질화)이라고 합니다.

이 비정질화가 이루어져야 annealing(열처리)로 인한 손상 회복이 쉽기 때문에 이와 같은 상태가 되도록 이온주입을 실시합니다.

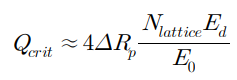

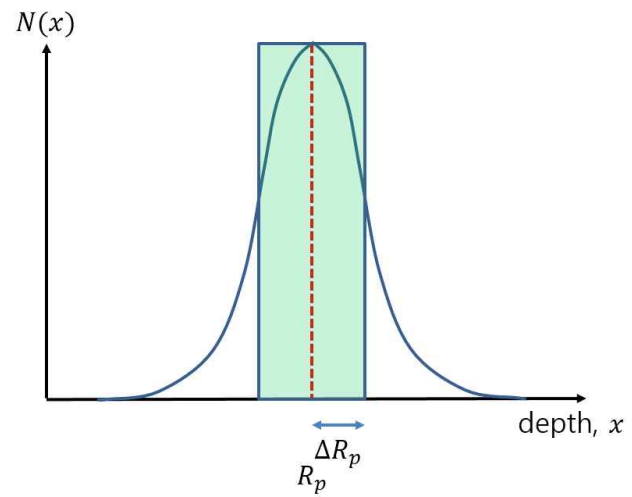

이 투사영역에서 비정질화가 되는 Dose의 양을 Critical Dose라고 합니다.

즉 Critical Dose를 맞은 기판의 모든 원자는 격자 이탈을 합니다.

입사이온의 면적을 A라고 하면, Dose Q에 의해 이탈되는 원자 수는 근사적으로

이고, 따라서

일 때 amorphiztion이 됩니다.

식을 다시 정리하면 다음과 같습니다.

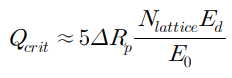

이 근사식에서 ion의 분포를 Gauss 분포 대신 사각형 분표로 가정하여 고려하면 최종 Creitical Dose는 다음과 같습니다.

5.5.2.1 Annealing(열처리)

이온 주입 후에는 많은의 격자결함 및 손상의 cluster 가 발생합니다. 이로 인해 다음과 같이 좋지 않은 현상을 야기합니다.

1. 전자, 정공 이 동도 (mobility) 감소로 인한 깊은 준위 형성 = 도핑활성도를 감소.

2. 소수 carrier의 life time 감소 = junction 누설전류를 증가.

따라서 열처리로 이런 손상을 줄여 회복시켜야 합니다. = annealing

온도는 약 40 0℃ ∼ 1000 ℃이며,

전기로 (furnace)에 의한 annealing 이 가장 일반적이 지만,

급속열처리 (rapid thermal annealing, RTA), 레이저 annealing 도 최근 많이 연구되고 있습니다.

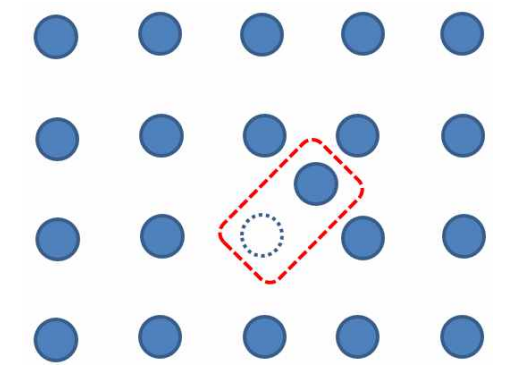

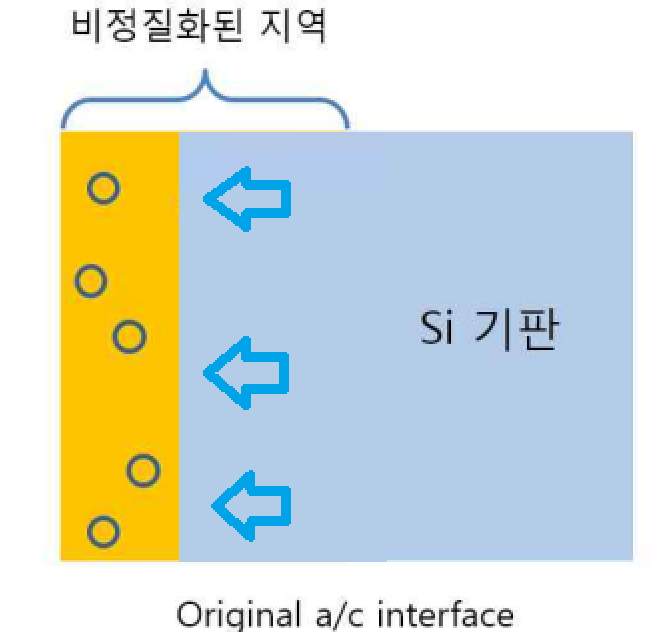

Amorphization 이 된 지역이 annealing에 의해

자기 자리로 되돌아가 격자가 재결정화 되기 시작하면

비정질, 결정 경계면 (a/c interface)가 화살표 방향으로 이동합니다.

그 외로

1. 이렇게 비정질화된 지역의 격자원자가 Si 기판의 원자배열에 맞추어 재결정화되는 것을

고상에피탁시 (solid phase epitaxy)라고 합니다.

2. 원래 a/c interface 에는 재결정화 후에도 어느 정도의 결정결함이 남아있는데 이것을

EOR (end of range) defect라고 합니다.

3. 이온 주입 시 상당한 열이 발생하게 됩니다. 그래서 국소적으로 결정화가 진행되는데(마치 마찰열) 이를

자체 열처리 효과(self annealing efect)라고 합니다.

*annealing을 할 때 이 결정화지역 근처에서는 이 결정덩어리의 배열을 닮아서 재 결정화되므로 최종적으로 polycrystal 이 되어 망한 기판이 됩니다.

그래서 냉각을 잘해주어야 합니다.

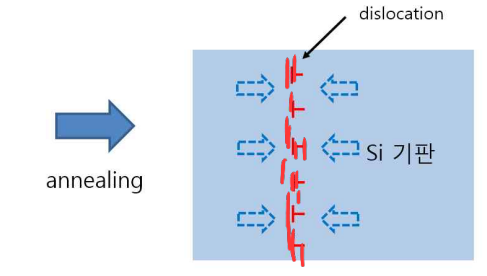

4. 만약 기판 표면과 내부만 결정화가 되어 있고,

중간만 비정질화가 되어있다면

열처리를 진행할 때 양쪽으로부터 재결정화가 진행되므로

결국 서로 닿는 지점의 원자배열이 어긋나 dislocation이 발생합니다.

amorphization의 재결정화 즉 solid phase epitaxy를 위해 annealing을 할 때,

고려해야 할 문제가 얼마나 많이 존재하는지 체감이 되시나요?

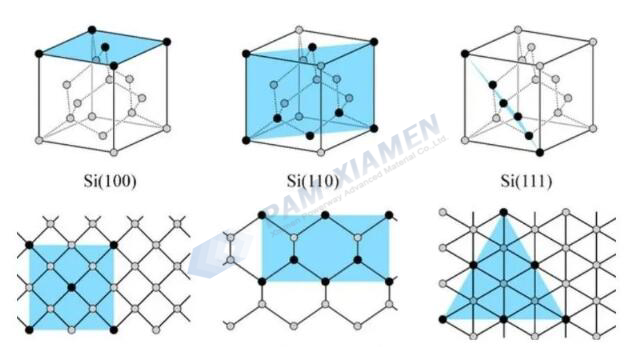

실리콘 기판의 재결정화 속도는 기판 방향에 따라 다릅니다.

(100)이 (111)의 10배 정도로 빠릅니다.

(100)의 면 간격은 격자상수 a.

(111)의 면간격은 a/√3으로

(100)의 면 간격이 더 크기 때문입니다.

5.1 이온전류

5.1로 잠시 되돌아 와서 보겠습니다.

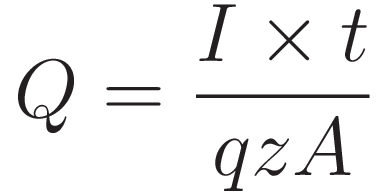

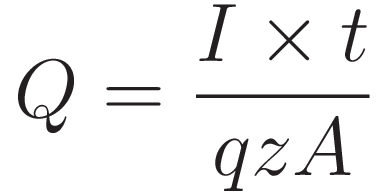

이온주입기는 하나의 회로를 구성하므로 이온주입과정에서 이온전류가 흐흡니다.

이 이온전류를 측정하여 dose을 결정할 수 있습니다.

이온전류를 I라고 하고 t 동안 면적이 A 인 웨이퍼에 이온주입을 하면 I×t/qz 은 총이 이온의 개수가 됩니다.. 여기서 이고 은 하전수이다. 단위면적당 총이 온의 개수가 dose 이므로 다음과 같이 쓸 수 있습니다.

q=1.602*106-19 C

z : 하전 수

이 식으로 Dose를 계산할 수 있습니다.

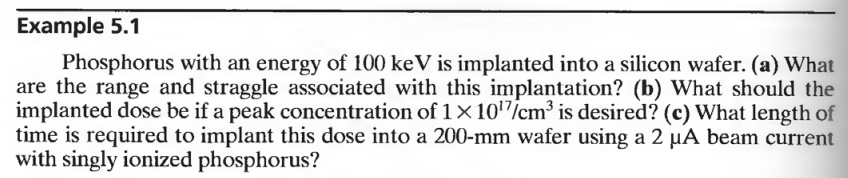

예제 5.1 )

이전 포스팅에서는 (a), (b)를 풀었습니다.

이번엔 이온 전류에 대해 배웠으니 (c)를 풀겠습니다.

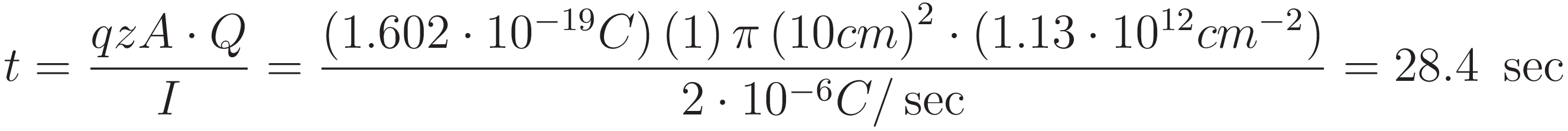

Solution (c):

해당 이온전류로 지름 200 mm 웨이퍼에 위 Dose를 주입하는 데에 걸리는 시간이 얼마인지 물어봅니다.

필요한 공식은 이온 전류에 의한 Dose 결정 식을 이용합니다.

질문에서 전류는 I = 2*10^-6C/sec

웨이퍼 지름이 200 mm 이므로 반지름 r = 10 cm

전하수는 z = 1

(b)의 값을 이용해야 합니다. Dose Q = 1.13*10^12 /㎠

이제 구할 수 있습니다.

이제 반도체공정 jaeger 책의 챕터 5가 끝났습니다.

문제를 풀 때는 단위 변환과 이해에 주의해야 합니다.

필자는 단순히 외우는 것이 아니라 이해하고 설명할 줄 알아야 진정하게 그 지식을 배웠다고 생각합니다.

긴 글 읽어 주셔서 감사합니다.

- 저자

- jaeger

- 출판

- 피어슨 에듀케이션

- 출판일

- 2013.08.30

'반도체 > 이온주입(implantation)' 카테고리의 다른 글

| Chapter 5.3~5.4 (이온주입) 주입 깊이, 핵저지, 전자저지 [반도체공정] feat.jaeger (0) | 2024.06.28 |

|---|---|

| Chapter 5.1~5.2 (이온주입) 주입범위, 예제 [반도체공정] feat.jaeger (0) | 2024.06.26 |