기술은 감각이다, 밀론 블로그

Chapter 5.3~5.4 (이온주입) 주입 깊이, 핵저지, 전자저지 [반도체공정] feat.jaeger 본문

Chapter 5.3~5.4 (이온주입) 주입 깊이, 핵저지, 전자저지 [반도체공정] feat.jaeger

milron 2024. 6. 28. 12:47반도체 8대 공정

1. 실리콘 웨이퍼 제조 공정

2. 산화공정(Oxidation)

3. 포토공정(Photo)

4. 식각공정(Etching)

5. 증착공정(Deposition)

6. 금속배선공정(Metalliztion)

7. EDS 공정(Electrical Die Sorting)

8. 패키지공정(Package)

5. 증착공정(Deposition) 목차

1. Chapter 5.1~5.2 (이온주입) 주입범위, 예제 [반도체공정] feat.jaeger

2. Chapter 5.3~5.4 (이온주입) 주입 깊이, 핵저지, 전자저지 [반도체공정] feat.jaeger

3. Chapter 5-5 (이온주입) Chaneling, Lattice damage, and annealing, 예제 [반도체공정] feat.jaeger

이온 주입을 진행한다면, 이온이 기판으로 주입되는 과정 속에서 어떤 현상이 발생하는지에 대한 지식과 이해가 중요합니다.

이번 포스팅에서 깊이(junction depth)와 핵저지, 전자저지에 대해 설명하겠습니다.

웨이퍼의 기판이 p형이라고 가정해봅시다.

기업에서는 기판 내부에 일정한 간격으로 n형 도핑을 원합니다.

우리는 이제 적절한 거리에 도핑할 n형 이온을 선택하고 도핑 깊이 즉, x_j(junction depth)를 구해야 합니다.

5.3 이온 선택 주입(ion selective prantation)

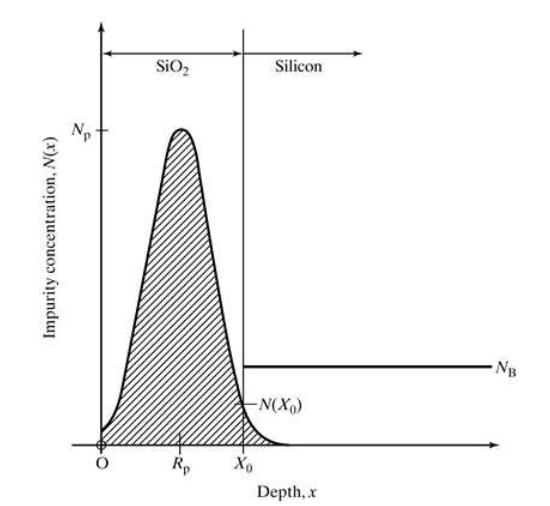

그림 5.5를 보면 그래프 상단에 SiO2와 Si가 보입니다.

각각 주입되는 산화막층, 기판층을 뜻합니다.

그래프 아래 N_B선이 보입니다.

주입되는 이온은 산화막 부분에만 존재해야합니다. Si 기판에 영향이 가면 절대로 안됩니다.

그러나 어느정도 이온이 기판에 침투하는 것을 완벽하게 방어하지는 못하므로,

기판에 영향이 가지 않을 정도의 적당한 침투만을 허용합니다.

그 기준이 되는 곳이 N_B입니다.

기판의 기본적인 도핑 농도인 이곳의 1할은 허용할 때, 즉 기판 농도 1/10 만큼의 침투를 허용해도 영향이 없다고 가정하면

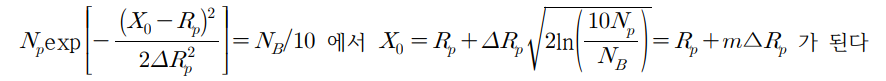

다음과 같이 계산 가능합니다.

5.4 xⱼ (junction depth)의 깊이

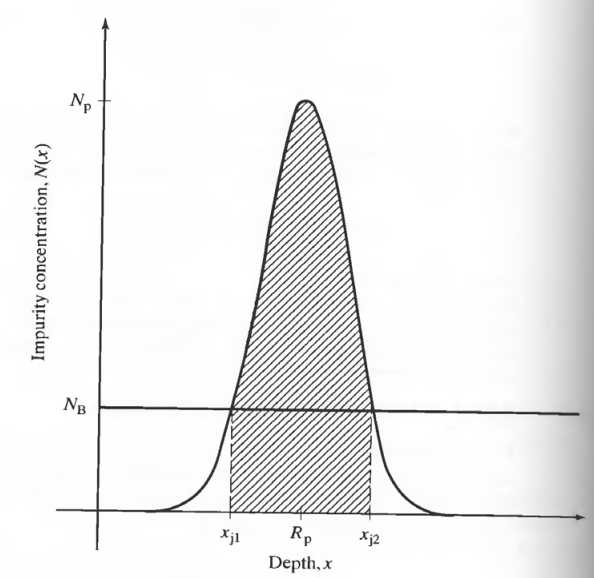

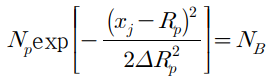

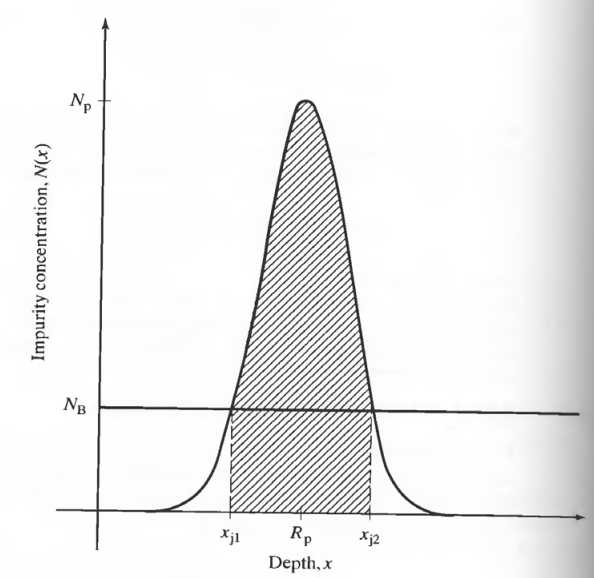

N_B의 도핑 농도를 가진 부분이 p형 기판의 농도라고 가정해봅시다.

이 도핑 농도 그래프의 함수 N(x)의 최고 지점이 Nₚ이고 우리가 n형 도핑해야할 부분입니다.

그래야 N_B > N(x) 인 지역에서 n형이 될 것입니다.

N_B : (background doping) 웨이퍼 기판이 가지는 기본적인 도핑농도

xⱼ : (junction depth) 이온 주입 도핑이 시작되는 범위

따라서 N > N(x) 인 지점에서 도핑 종류가 달라집니다.

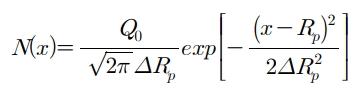

이전 포스팅에서 5.2부분의 가우스 정규 분포식을 다시 봅시다.

만약 N(x) = Nₚ 이면 x = xⱼ 로 결정할 수 있고

가 됩니다.

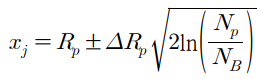

자연로그로 정리하면 다음과 같이 junction depth 식이 유도됩니다.

그림을 다시 보면 junction depth가 2군데 존재하게 됩니다.(figure 5.6)

반도체 IC 공정에서는 반드시 특정 지역에서만 이온이 주입되어야 합니다.

애초에 이온 주입 방식은 어떤 물질이든 상관없이 물리적인 힘으로 기판을 뚫고 들어갑니다.

따라서 mask를 잘 설계해야합니다.

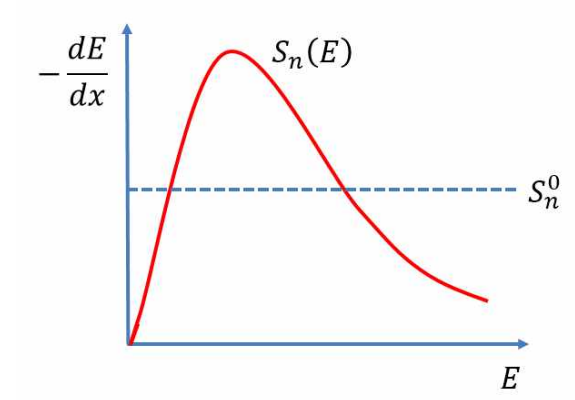

핵저지(nuclear stopping)

주입되는 이온은 기판 내부로 운동량을 가지며 침투합니다.

이때 기판 원자와 물리적 충돌이 발생하여 저지됩니다.

즉 핵저지란 불순물 이온이 표적 기판의 원자에 에너지를 전달하는 탄성충돌을 말합니다.

이 핵저지에서 에너지를 전달받은 기판의 원자는 자기 자리를 이탈하게 되는 현상이 발생하게 됩니다.

즉 격자 결함이 발생하게 됩니다.

이 에너지에 대한 손실율은 다음과 같은 그래프를 띕니다.

에너지 변화가 없는 근사적인 핵 정지력 S^0_n을 가정하면 일정한 에너지의 손실율만 가지게 됩니다.

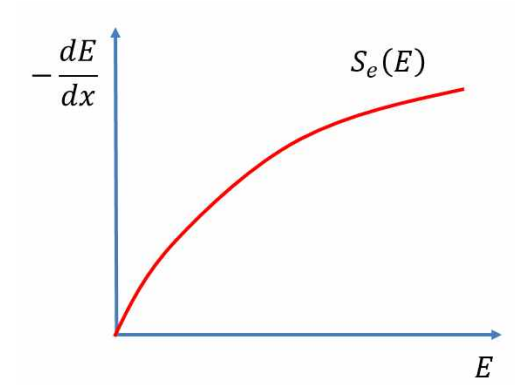

전자저지 (electronic stopping)

이온과 전자 간의 충돌은 비탄성 충돌에 의한 것으로 양자역학적 계산이 필요합니다.

큰 에너지를 받아 자유전자가 되어버리거나,

E_v(valence band)에서 E_c(cunduction band)로 여기시킵니다.

여기된 전자는 바닥상태로 이동하여 에너지를 소비하며 빛 혹은 열을 발생시킵니다.

손실율 그래프는 다음과 같습니다.

전자정지력은 에너지 제곱근에 비례합니다.

여기서

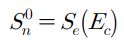

인 에너지 E_c를 critical energy라고 부릅니다.

이제 핵저지와 전자저지 효과를 같이 나타내 보면,

핵정지력 변화가 없는 근사 값인 S^0_n인 critical energy 보다 입사 에너지가

낮다면 전자저지의 영향이 더 크고,

크다면 핵저지의 영향이 더 크게 됩니다.

다음 포스팅은 ion channeling 효과와 격자 손상에 대해 이야기 하겠습니다.

긴글 봐주셔서 감사합니다.

- 저자

- jaeger

- 출판

- 피어슨 에듀케이션

- 출판일

- 2013.08.30

'반도체 > 이온주입(implantation)' 카테고리의 다른 글

| Chapter 5-5 (이온주입) Chaneling, Lattice damage, and annealing, 예제 [반도체공정] feat.jaeger (0) | 2024.06.30 |

|---|---|

| Chapter 5.1~5.2 (이온주입) 주입범위, 예제 [반도체공정] feat.jaeger (0) | 2024.06.26 |