기술은 감각이다, 밀론 블로그

대학발표주제 - 이온주입을 이용한 GaN on Si 소자 항복전압 개선 [한국원자력연구원 특허] 본문

발표 ppt는 글 맨 아래 올려두었습니다.

GaN on Si 소자 관련 팀별 5분 개인 발표를 학교에서 진행한 적이 있는데, 저는 한국원자력연구원의 특허자료를 인용해 발표를 하였습니다.

발표 내용은 이온주입을 이용한 GaN on Si 소자 항복전압 개선입니다.

관련 기술 조사 중 GaN on Si 관련 기술이 뭐가 있을까 고민을 좀 했습니다.

워낙 다양한 기술이 존재했기 때문인데, 그래서 저는 GaN on Si 소자의 문제점에 집중했습니다.

GaN과 Si는 격자 상수의 차이와 열팽창 계수의 차이가 존재합니다.

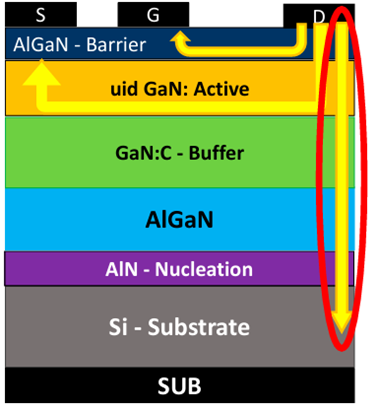

따라서 이를 완화하기 위해서 GaN-Si 물질 사이에 AlN이라는 박막을 버퍼층으로 성장합니다.

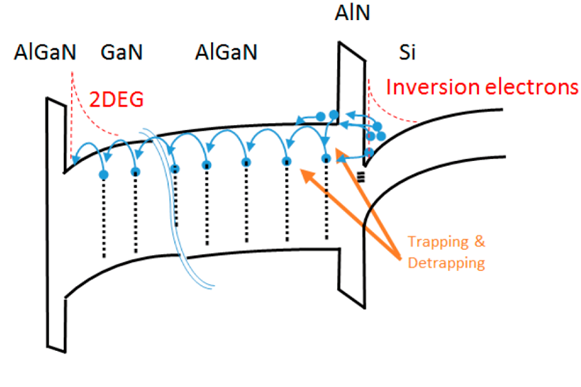

이 버퍼층과 기판 사이 장벽에서 어떤 문제점이 발생하게 됩니다.

AlN의 밴드갭은 6.1 eV

Si의 밴드갭은 1.1 eV

두 장벽 간의 밴드갭 차이가 어마어마합니다.

따라서 두 밴드 계면 사이의 small gab으로 인해 tunnealing이 일어나는 avalanche breackdown이 발생할 수 있습니다.

즉 수직전류에 의한 누설전류가 발생하게 되는 것입니다.

이 현상을 해결하려면 소자의 항복전압을 개선해야 합니다.

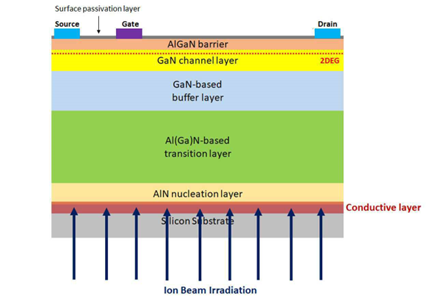

본 특허에서는 GaN on Si 소자 기판에 이온 조사를 통하여 소자의 항복전압을 개선하고자 하는 기술을 설명합니다.

GaN on Si 소자는 높은 항복전압(3 Mev/cm)과 큰 밴드갭(3.4 eV), 많은 전자 농도(2DEG)를 가지고 있다는 장점이 있습니다.

그러나 비싸고 제작이 어렵습니다.

또한 문제점이 여럿 존재하는데 서론에서 설명한 바와 같이 다음과 같이 존재합니다.

- 격자 상수 차이

- 열팽창 계수 차이

고품질 박막을 성장하기 위해 일반적으로 AlN 박막을 버퍼층으로 이용합니다.

여기서 문제가 발생합니다.

- AlN 버퍼층과 Si 기판 간의 높은 밴드갭 차이.

- 실리콘으로부터 공급되는 전자들(inversion electron channel)

이 두 가지 요소로 인해 고농도의 전하가 AlN-Si 게면에 집적됩니다.

즉 Cunductive layer(전도성층)이 형성됩니다.

이때 수백 전압이상의 고전압이 인가되면 전도성층에 의해 수직으로 누설전류가 흐르게 됩니다.

이것은 소자의 손상을 뜻합니다.

소자가 손상을 입게 되면 breakdown voltage를 향상하는 데에 한계가 존재하게 됩니다.

따라서 이 항복전압을 개선시키기 위해 누설전류를 막아내야 합니다.

방법은 여러 가지가 존재하나 그 방법들도 문제점과 단점이 존재하여 구체적인 방법이 없는 걸로 알고 있습니다.

본 특허에 의하면 본 소자의 기판에 입자빔을 조사하여 AlN 박막과 Si 기판 계면에 입자 이온을 집중적으로 분포시켜 저항을 커지게 하여 소자 손상 없이 누설전류 발생원인을 제거함으로써 항복전압을 개선시키는 방법을 소개합니다.

다양한 이온 입자빔이 존재하나 양성자 빔이 이동하며 발생하는 결함이 가장 적고 원하는 위치에 도핑이 가능합니다.

이온 주입 과정에서 생기는 Frenkel defect와 같은 격자 결함이 발생하게 되지만 annealing으로 재결정화 시켜 해결이 가능합니다.

이온주입 결함 참고글

Chapter 5-5 (이온주입) Chaneling, Lattice damage, and annealing, 예제 [반도체공정] feat.jaeger

반도체 8대 공정1. 실리콘 웨이퍼 제조 공정2. 산화공정(Oxidation)3. 포토공정(Photo)4. 식각공정(Etching)5. 증착공정(Deposition)6. 금속배선공정(Metalliztion)7. EDS 공정(Electrical Die Sorting)8. 패키지공정(Package)

milronmusk.tistory.com

필자의 발표 ppt는 아래 올려두었습니다.

필요하신 분은 댓글남겨주시면 암호 알려드리겠습니다.

Reference

한국원자력연구원, “GaN계 전력 소자의 제조 방법 및 이에 따라 제조된 GaN계 전력 소자”, 특허 출원번호, 1020200159070, 출원일 2020.11.24, 등록일 2022.10.12)

사진 참고자료 :

https://doi.org/10.3390/mi11010101,

https://www.mdpi.com/2072-666X/12/11/1284

AlN-Si 간 전도성층에 대한 설명 :

M. Borga, et al., “Impact of Substrate Resistivity on the Vertical Leakage, Breakdown, and Trapping in GaN-on-Si E-Mode HEMTs,” IEEE Trans. Electron Devices, Vol. 65, pp. 2765-2770, 2018,

고저항성 실리콘 기판의 강한 트래핑에 대한 설명 :